Найден новый способ «уплотнения» чипов без смены техпроцесса

Команда исследователей Samsung Electronics совместно с американскими технологическими университетами нашла альтернативный способ увеличения плотности транзисторов на одном кристалле. Учёные разработали метод, позволяющий размещать дополнительный слой микросхем на уже готовом чипе.

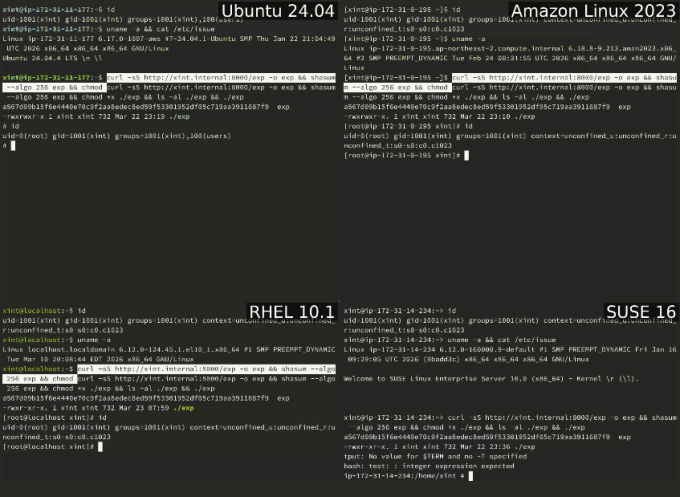

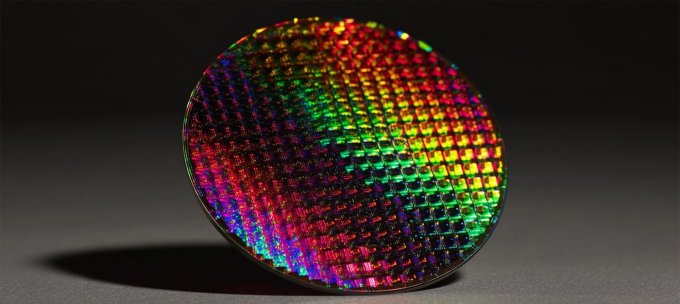

При изготовлении CMOS-чипов на кремниевую пластину последовательно наносятся несколько слоёв: собственно транзисторы, а затем различные металлы и изоляторы для питания и формирования логических ячеек.

Количество слоёв обычно ограничено — все дополнительные окажутся крайне чувствительными к температурам, применяемым в производственном процессе. Поэтому стандартный процесс «дублирования» слоя транзисторов попросту разрушит нижний слой при нанесении нового.

Новый научный подход в теории способен решить эту проблему. Учёные использовали сверхтонкий слой аморфного оксида индия толщиной всего 2 нанометра для изоляции дополнительных транзисторов. Этот материал требует значительно более низкой температуры обработки по сравнению с традиционными решениями, что предотвращает повреждение предыдущего слоя транзисторов от нагрева.

В результате исследователям удалось повысить плотность транзисторов чипа. В перспективе такое решение может заметно увеличить лимит плотности транзисторов, улучшив вычислительную мощность чипов без перехода на новые техпроцессы. Впрочем, технология ещё требует доработки и пока не готова к коммерческому использованию.