Учёные впервые уложили шесть КМОП-транзисторов друг на друга

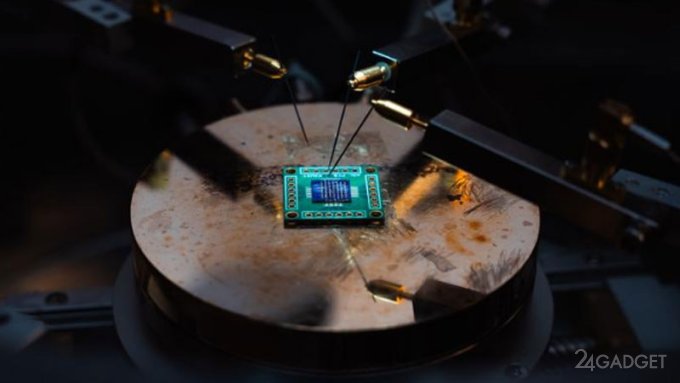

Группа учёных из Университета науки и технологий имени короля Абдаллы (KAUST, Саудовская Аравия) установила рекорд в производстве чипов, создав первую в мире шестиуровневую гибридную КМОП-схему (комплементарную структуру). Ранее рекорд принадлежал бельгийскому центру Imec, разработавшему двухуровневую конструкцию CFET. Разработчики микросхем ограничены площадью кристаллов, и размещение транзисторов «друг у друга на голове» — один из способов шагнуть дальше.

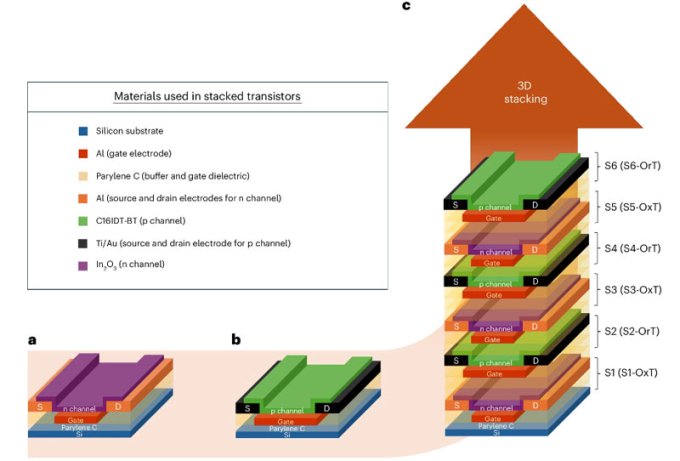

О разработке рассказано в статье в журнале Nature Electronics. Схема сочетает транзисторы n-типа — оксидные тонкоплёночные (OxTs) и p-типа — органические тонкоплёночные транзисторы (OrTs), предназначенные для массового производства электроники, включая гибкие дисплеи, носимые сенсоры и устройства Интернета вещей.

Авторы подчёркивают растущий спрос на интегральные схемы с низким энергопотреблением, механической гибкостью и возможностью масштабного производства, где традиционное горизонтальное расположение цепей и элементов сталкивается с ограничениями по разрешению и стоимости. Вертикальная интеграция позволяет увеличить плотность транзисторов, сократить длину соединений и минимизировать паразитные задержки, при этом укладываясь в рамки низкотемпературных процессов производства, что критично для ряда материалов, а также для многослойных чипов, склонных к перегреву из-за высокой плотности мощности.

Предыдущие работы ограничивались двумя слоями из-за проблем с выравниванием соединяемых поверхностей и перегрева многослойных решений. Однако предлагаемая платформа преодолевает эти барьеры, демонстрируя рекордные шесть транзисторных стеков с 41 технологическим слоем.

Изготовление шестислойной структуры осуществлялось в рамках 40-этапного литографического процесса на кремниевых подложках, начиная с буферного изоляционного слоя толщиной 2 мкм. Электроды (Al для OxTs и Ti/Au для OrTs) осаждались методом физического осаждения из паровой фазы (PVD) при низкой мощности для минимизации шероховатости (<1 нм). Весь процесс выполнялся при комнатной температуре или нагреве не выше 100 °C, чтобы избежать термических повреждений нижних слоёв. Размеры транзисторов варьировались: длина затвора для n-типа составляла 10 мкм, для p-типа — 3 мкм, при этом чередование типов обеспечивало баланс токов.

Характеристики транзисторов оценивались на 600 устройствах (по 100 на стек), показав лучшие результаты у нижних слоёв. Созданные на основе опытных массивов гибридные инверторы (300 шт.) достигли максимального коэффициента усиления 94,84 В/В, напряжения переключения 0,93–2,61 В и энергопотребления 0,47 мкВт. Также были протестированы логические элементы на основе шестиуровневых транзисторов — в частности, элементы NOR и другие.

Предлагаемая платформа открывает путь к созданию высокоплотных и энергоэффективных схем для крупномасштабной электроники, превосходя предыдущие двухслойные аналоги по плотности и производительности. Повышение качества соединения слоёв и использование низкотемпературных процессов обеспечивают совместимость с гибкими подложками, снижая паразитные эффекты и повышая пропускную способность. Авторы подчёркивают потенциал своей разработки для производства логики, памяти и сенсоров, что может революционизировать сферу энергоэффективных решений. Дальнейшие исследования будут сосредоточены на оптимизации верхних слоёв и интеграции с крупными подложками, что необходимо для подготовки коммерческих продуктов.