ИИ-агент спроектировал полноценный процессор на RISC-V за 12 часов — промпт содержал всего 219 слов (2 фото)

Стартап Verkor.io, специализирующийся на разработке чипов с использованием искусственного интеллекта, в исследовательской статье, опубликованной в марте, рассказал, как его агентная система ИИ Design Conductor самостоятельно создала полноценное ядро процессора на архитектуре RISC-V. Для этого потребовалось всего 12 часов: система взяла за основу документ с запросом из 219 слов и сгенерировала проверенную, готовую к компоновке схему, что на несколько порядков быстрее стандартных сроков разработки коммерческих чипов, которые составляют от 18 до 36 месяцев.

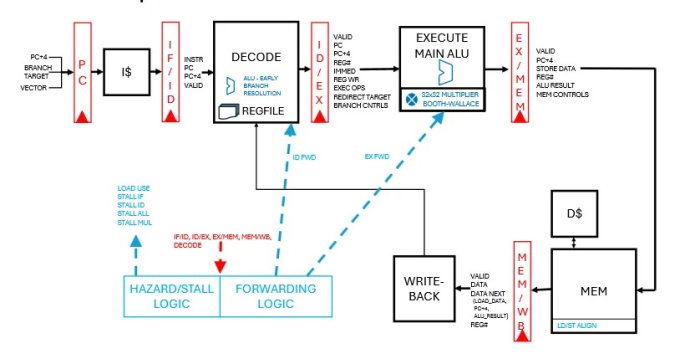

По словам Verkor, это первый случай, когда автономный агент создал работающий процессор — от спецификации до файла компоновки GDSII. В результате получился процессор VerCore — пятиступенчатое конвейерное ядро с последовательным выполнением команд и однопоточной обработкой, которое при тактовой частоте 1,48 ГГц на 7-нанометровом техпроцессе ASAP7 набрало 3261 балл в тесте CoreMark.

В статье Verkor подробно описана конвейерная архитектура, включающая этапы выборки, декодирования, выполнения, обращения к памяти и обратной записи команд, а также раннее разрешение ветвлений и переадресацию операндов. В ходе оптимизации система самостоятельно реализовала быстрый умножитель Бута — Уоллеса с тактовой частотой 2,57 ГГц и схему с однотактным штрафом за ветвление, которую агент выбрал после реализации и тестирования одно- и двухтактных вариантов. Verkor сравнивает производительность VerCore в тесте CoreMark с производительностью мобильного процессора Intel Celeron SU2300 2011 года на базе архитектуры Penryn.

Пятиступенчатое ядро с последовательным выполнением команд, без кеша и внеочередного выполнения команд — довольно простая конструкция по отраслевым стандартам. В статье Verkor отмечается, что стоимость разработки передовых чипов превышает $400 млн, на их разработку уходит от 18 до 36 месяцев, при этом в разработке участвуют сотни инженеров. VerCore гораздо проще этих чипов. Тем не менее 12 часов, затраченные на полностью автономный процесс от спецификации до компоновки, — это впечатляющий результат, даже несмотря на то, что для этого потребовалось «множество десятков миллиардов токенов» при сравнительно невысоком уровне сложности.

VerCore не был изготовлен физически: вместо этого его работоспособность была проверена с помощью Spike — эталонного симулятора RISC-V ISA. ASAP7 — это комплект для разработки академических технологических процессов, а не коммерческий 7-нм техпроцесс. В Verkor утверждают, что VerCore может запускать вариант uCLinux в симуляторе.

В статье Verkor честно говорится об ограничениях базовых языковых моделей и отмечается, что ИИ-агент иногда «недооценивает сложность работы, необходимой для решения тех или иных проблем». Например, в одном случае, когда не удавалось уложиться в сроки, Design Conductor пытался внести серьёзные изменения, чтобы «углубить процесс проектирования» вместо поиска более простых решений. В другом случае исследователи заметили, что модель рассуждала о Verilog — событийно-ориентированном языке — как о последовательном коде. «Хотя мы обнаружили, что это не повлияло на способность Design Conductor обеспечивать функциональную корректность, из-за этого Design Conductor стало сложнее устранять проблемы с соблюдением сроков», — пояснили исследователи.

По оценкам исследователей, чтобы довести систему до состояния, готового к серийному производству, потребуется от пяти до десяти специалистов. Кроме того, с ростом сложности проекта требования к вычислительным мощностям увеличиваются нелинейно, что делает весь процесс менее практичным в коммерческом масштабе. В Verkor сообщили, что планируют опубликовать исходный код VerCore и скрипты для сборки к концу апреля, а также продемонстрировать реализацию на ПЛИС на мероприятии DAC — ежегодной конференции по автоматизации проектирования электронных устройств.

В предыдущих проектах по разработке чипов с использованием искусственного интеллекта, таких как проект китайских исследователей, которые в 2023 году создали процессор на архитектуре RISC-V менее чем за пять часов, и более поздний проект QiMeng, использовались другие методологии и архитектуры. Design Conductor от Verkor самостоятельно выполняет весь процесс проектирования — от спецификации до GDSII.

Источник: arxiv